# HD6845R/HD6845S - CRT Controller (CRTC)

The CRTC is a LSI controller which is designed to provide an interface for microcomputers to raster scan type CRT displays. The CRTC belongs to the HD6800 LSI Family and has full compatibility with MPU in both data lines and control lines. Its primary function is to generate timing signal which is necessary for raster scan type CRT display according to the specification programmed by MPU. The CRTC is also designed as a programmable controller, so applicable to wide-range CRT display from small low-functioning character display up to raster type full graphic display as well as large high-functioning limited graphic display.

#### **FEATURES**

- Number of Displayed Characters on the Screen, Vertical Dot Format of One Character, Horizontal and Vertical Sync Signal, Display Timing Signal are Programmable

- 3.7 MHz High Speed Display Operation (HD6845S)

- 3.0 MHz High Speed Display Operation (HD6845R)

- · Line Buffer-less Refreshing

- 14-bit Refresh Memory Address Output (16k Words max. Access)

- Programmable Interface/Non-interface Scan Mode

- Built-in Cursor Control Function

- · Programmable Cursor Height and its Blink

- Built-in Light Pen Detection Function

- · Paging and Scrolling Capability

- TTL Compatible

- Single + 5V Power Supply

#### ORDERING INFORMATION

| CRTC                            | Bus Timing                    | CRT Display<br>Timing |

|---------------------------------|-------------------------------|-----------------------|

| HD6845S<br>HD68A45S<br>HD68B45S | 1.0 MHz<br>1.5 MHz<br>2.0 MHz | 3.7 MHz max.          |

| HD6845R<br>HD68A45R<br>HD68B45R | 1.0 MHz<br>1.5 MHz<br>2.0 MHz | 3.0 MHz max.          |

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                  | Symbol            | Value              | Unit |

|-----------------------|-------------------|--------------------|------|

| Supply Voltage        | V <sub>cc</sub> * | -0.3 ~ +7.0        | V    |

| Input Voltage         | V <sub>in</sub> * | -0.3 ~ +7.0        | V    |

| Operating Temperature | Topr              | <b>- 20 ∼ + 75</b> | °c   |

| Storage Temperature   | T <sub>sto</sub>  | - 55 ~ +150        | °c   |

With respect to V<sub>SS</sub> (SYSTEM GND)

[NOTE] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Item                  | Symbol            | min  | typ | max             | Unit |

|-----------------------|-------------------|------|-----|-----------------|------|

| Supply Voltage        | V <sub>cc</sub> * | 4.75 | 5.0 | 5.25            | V    |

|                       | V <sub>IL</sub> * | -0.3 | -   | 0.8             | V    |

| Input Voltage         | V <sub>IH</sub> * | 2.0  | _   | V <sub>cc</sub> | V    |

| Operating Temperature | T <sub>opr</sub>  | - 20 | 25  | 75              | °c   |

<sup>.</sup> With respect to VSS (SYSTEM GND)

#### ■ ELECTRICAL CHARACTERISTICS

• DC CHARACTERISTICS ( $V_{CC}$  = 5V ± 5%,  $V_{SS}$  = 0V, Ta = -20 $\sim$ +75 $^{\circ}$ C, unless otherwise noted.)

| Item                                  | Symbol          | Test C                                                  | Condition                             | min  | typ*         | max             | Unit     |  |

|---------------------------------------|-----------------|---------------------------------------------------------|---------------------------------------|------|--------------|-----------------|----------|--|

| Input "High" Voltage                  | V <sub>IH</sub> |                                                         |                                       | 2.0  | -            | V <sub>cc</sub> | V        |  |

| Input "Low" Voltage                   | VIL             |                                                         |                                       | -0.3 |              | 0.8             | V        |  |

| Input Leakage Current                 | l <sub>in</sub> | V <sub>in</sub> = 0 ~ 5.25                              | V (Except Do~D7)                      | -2.5 | _            | 2.5             | μА       |  |

| Three-State Input Current (off-state) | ITSI            | V <sub>in</sub> = 0.4 ~ 2.<br>V <sub>CC</sub> = 5.25V ( |                                       | - 10 | _            | 10              | μΑ       |  |

| Output "High" Voltage                 | V               | I <sub>LOAD</sub> = -205                                | μΑ (D <sub>0</sub> ~ D <sub>7</sub> ) | 2.4  |              | _               | v        |  |

| Output High Voltage                   | VoH             | I <sub>LOAD</sub> = -100                                | μΑ (Other Outputs)                    | 2.4  | <del>-</del> |                 | <u> </u> |  |

| Output "Low" Voltage                  | VoL             | I <sub>LOAD</sub> = 1.6 m                               | A                                     | -    |              | 0.4             | V        |  |

|                                       |                 | V <sub>in</sub> = 0                                     | $D_0 \sim D_7$                        | -    | -            | 12.5            | pF       |  |

| Input Capacitance                     | Cin             | Ta = 25°C<br>f = 1.0 MHz                                | Other Inputs                          | -    | _            | 10.0            | pF       |  |

| Output Capacitance                    | Cout            | V <sub>in</sub> = 0V, Ta =                              | 25°C, f = 1.0 MHz                     | -    |              | 10.0            | pF       |  |

| Power Dissipation                     | PD              |                                                         |                                       | _    | 600          | 1000            | mW       |  |

<sup>\*</sup> Ta =  $25^{\circ}$ C,  $V_{CC}$  = 5.0V

----- HD6845R/HD6845S

#### • AC Characteristics ( $V_{CC}$ = 5V $\pm$ 5%, $T_a$ = -20 $\sim$ +75°C, unless otherwise noted.)

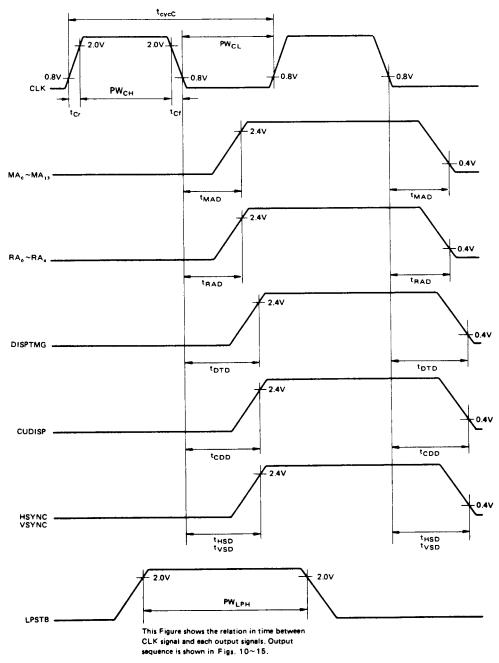

### 1. TIMING OF CRTC SIGNAL

|     |                                    |                                   | Test      | Н   | D6845 | 7   | Н        | S   | Unit |      |  |

|-----|------------------------------------|-----------------------------------|-----------|-----|-------|-----|----------|-----|------|------|--|

| No. | Item                               | Symbol                            | Condition | min | typ   | max | min      | typ | max  | Unit |  |

| 1   | Clock Cycle Time                   | t <sub>cycC</sub>                 |           | 330 | -     |     | 270      | -   | _    | ns   |  |

| 2   | Clock "High" Pulse Width           | PW <sub>CH</sub>                  |           | 150 | _     |     | 130      |     |      | ns   |  |

| 3   | Clock "Low" Pulse Width            | PW <sub>CL</sub>                  |           | 150 | _     |     | 130      |     |      | ns   |  |

| 4   | Rise and Fall Time for Clock Input | T <sub>Cr</sub> , t <sub>Cf</sub> | Fig. 1    | _   |       | 15  |          |     | 20   | ns   |  |

| - 5 | Horizontal Sync Delay Time         | t <sub>HSD</sub>                  |           | _   | -     | 250 |          |     | 200  | ns   |  |

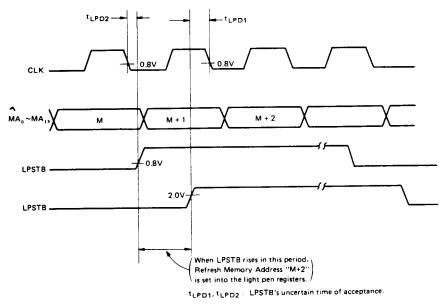

| 6   | Light Pen Strobe Pulse Width       | PWLPH                             |           | 80  | _     | _   | 60       |     |      | ns   |  |

|     | Light Pen Strobe                   | t <sub>LPD1</sub>                 | -         | -   | _     | 80  |          | _   | 70   | ns   |  |

| 7   | Uncertain Time of Acceptance       | t <sub>LPD2</sub>                 | Fig. 2    | _   |       | 10  | _        |     | 0    | ns   |  |

| 8   | Memory Address Delay Time          | t <sub>MAD</sub>                  |           | _   | _     | 160 |          | _   | 160  | ns   |  |

| 9   | Raster Address Delay Time          | t <sub>RAD</sub>                  | 1         | _   | _     | 160 | <u> </u> |     | 160  | ns   |  |

| 10  | DISPTMG Delay Time                 | t <sub>DTD</sub>                  | Fig. 1    | _   | _     | 250 |          |     | 250  | ns   |  |

| 11  | CUDISP Delay Time                  | t <sub>CDD</sub>                  | 1         |     | -     | 250 | _        |     | 250  | ns   |  |

| 12  | Vertical Sync Delay Time           | t <sub>VSD</sub>                  |           |     | _     | 250 |          |     | 250  | ns   |  |

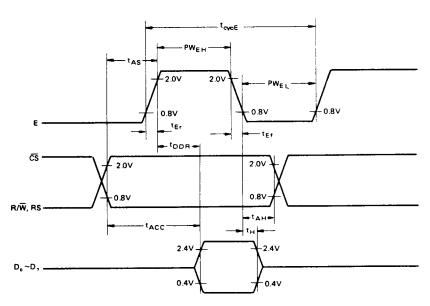

#### 2. MPU READ TIMING

|                           |                   | Test      |      | HD6845F<br>HD68459 |     |       | D68A45<br>D68A45 |     |      | D68B45 |     | Unit  |

|---------------------------|-------------------|-----------|------|--------------------|-----|-------|------------------|-----|------|--------|-----|-------|

| Item                      | Symbol            | Condition | min  | typ                | max | min   | typ              | max | min  | typ    | max | Oiiit |

| Enable Cycle Time         | t <sub>cycE</sub> |           | 1.0  | -                  | _   | 0.666 | _                |     | 0.5  |        |     | μς    |

| Enable "High" Pulse Width | PWEH              |           | 0.45 | _                  | _   | 0.28  |                  |     | 0.22 | -      |     | μς    |

| Enable "Low" Pulse Width  | PWEL              |           | 0.40 | -                  | -   | 0.28  | -                |     | 0.21 |        |     | μς    |

| Enable Rise and Fall Time | ter, ter          |           |      | -                  | 25  |       | _                | 25  |      |        | 25  | ns    |

| Address Set Up Time       | tas               | Fig. 3    | 140  | -                  | -   | 140   | _                |     | 70   |        |     | ns    |

| Data Delay Time           | tope              | _         | _    | _                  | 320 | _     | _                | 220 |      |        | 180 | ns    |

| Data Hold Time            | t <sub>H</sub>    |           | 10   |                    | _   | 10    | -                | -   | 10   |        |     | ns    |

| Address Hold Time         | t <sub>AH</sub>   | 1         | 10   | _                  | -   | 10    | _                | -   | 10   | -      |     | ns    |

| Data Access Time          | tACC              | 1         | _    | -                  | 460 | _     | -                | 360 | _    |        | 250 | ns    |

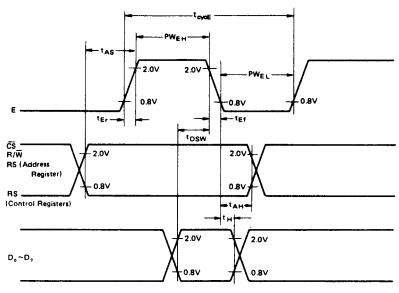

#### 3. MPU WRITE TIMING

|                           |                  | Test<br>Condition | HD6845R<br>HD6845S |     |          | HD68A45R<br>HD68A45S |     |     | <br> | Unit |     |    |

|---------------------------|------------------|-------------------|--------------------|-----|----------|----------------------|-----|-----|------|------|-----|----|

| Item                      | Symbol           |                   | min                | typ | max      | min                  | typ | max | min  | typ  | max | 0  |

| Enable Cycle Time         | teyce            |                   | 1.0                | -   |          | 0.666                |     |     | 0.5  | -    |     | μs |

| Enable "High" Pulse Width | PWEH             |                   | 0.45               | _   | -        | 0.28                 | _   | -   | 0.22 | _    |     | μs |

| Enable "Low" Pulse Width  | PWEL             |                   | 0.40               | _   | -        | 0.28                 | _   |     | 0.21 |      |     | μs |

| Enable Rise and Fall Time | ter, ter         | <b>.</b> .        | _                  | _   | 25       | _                    | _   | 25  | _    |      | 25  | ns |

| Address Set Up Time       | tas              | Fig. 4            | 140                | _   |          | 140                  |     |     | 70   |      |     | ns |

| Data Set Up Time          | t <sub>DSW</sub> |                   | 195                | -   |          | 80                   |     |     | 60   |      |     | ns |

| Data Hold Time            | t <sub>H</sub>   | 1                 | 10                 | -   | <b>-</b> | 10                   | _   |     | 10   |      |     | ns |

| Address Hold Time         | t <sub>AH</sub>  | 1                 | 10                 | -   | _        | 10                   | -   | -   | 10   | -    | -   | ns |

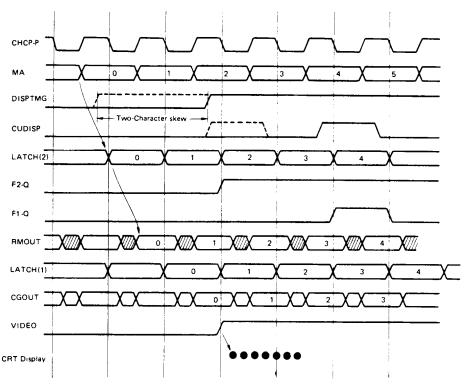

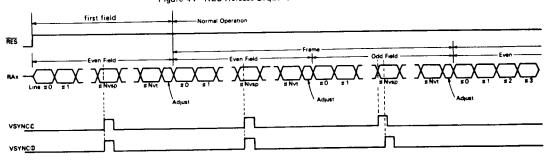

Figure 1 Time Chart of the CRTC

Figure 2 LPSTB Input Timing & Refresh Memory Address that is set into the light pen registers.

Figure 3 Read Sequence

Figure 4 Write Sequence

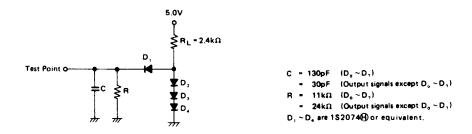

Figure 5 Test Loads

#### SYSTEM DESCRIPTION

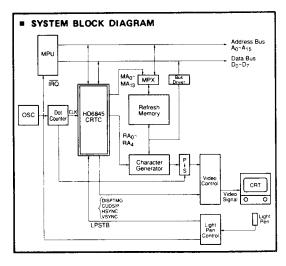

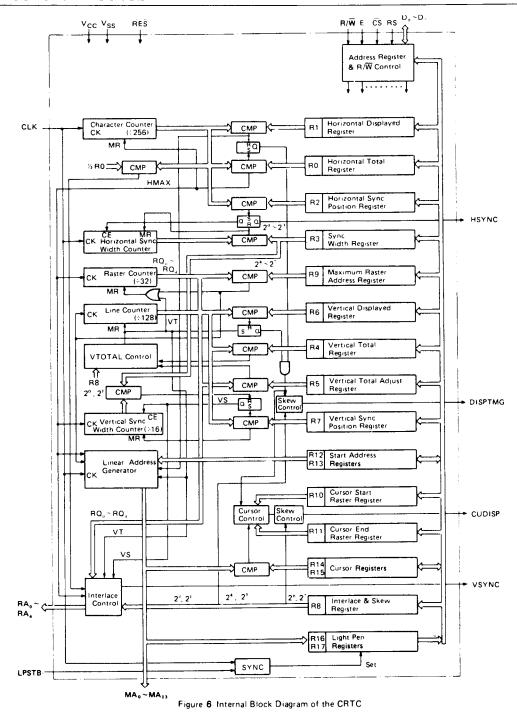

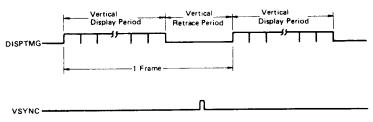

The CRTC is a LSI which is connected with MPU and CRT display device to control CRT display. The CRTC consists of internal register group, horizontal and vertical timing circuits, linear address generator, cursor control circuit, and light pen detection circuit. Horizontal and vertical timing circuit generate RA<sub>0</sub>~RA<sub>4</sub>, DISPTMG, HSYNC, and VSYNC. RA<sub>0</sub>~RA<sub>4</sub> are raster address signals and used as input signals for Character Generator. DISPTMG, HSYNC, and VSYNC signals are received by video control circuit. This horizontal and vertical timing circuit consists of internal counter and comparator circuit.

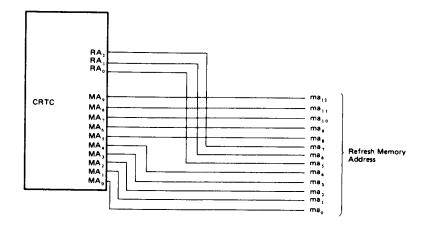

Linear address generator generates refresh memory address MA<sub>0</sub> ~MA<sub>13</sub> to be used for refreshing the screen. By these address signals, refresh memory is accessed periodically. As 14 refresh memory address signals are prepared, 16k words max are accessible. Moreover, the use of start address register enables paging and scrolling. Light pen detection circuit detects light pen position on the screen. When light pen strobe signal is received, light pen register memorizes linear address generated by linear address generator in order to memorize where light pen is on the screen. Cursor control circuit controls the position of cursor, its height, and its blink.

## 2

#### # FUNCTION OF SIGNAL LINE

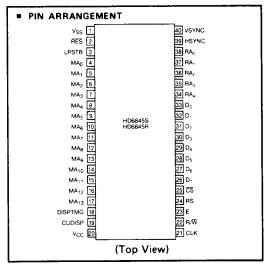

The CRTC provides 13 interface signals to MPU and 25 interface signals to CRT display.

## • Interface Signals to MPU Bi-directional Data Bus ( $D_0 \sim D_7$ )

I/O Pin No. 33 ~ 26

Bi-directional data bus  $(D_0 \sim D_7)$  are used for data transfer between the CRTC and MPU. The data bus outputs are 3-state buffers and remain the high-impedance state except when MPU performs a CRTC read operation.

#### Read/Write (R/W)

Input Pin No. 22

Read/Write signal  $(R/\overline{W})$  controls the direction of data transfer between the CRTC and MPU. When  $R/\overline{W}$  is at "High" level, data of CRTC is transferred to MPU. When  $R/\overline{W}$  is at "Low" level, data of MPU is transferred to CRTC.

#### Chip Select (CS)

Input Pin No. 25

Chip Select signal (CS) is used to address the CRTC. When CS is at "Low" level, it enables Read/Write operation to CRTC internal registers. Normally this signal is derived from decoded address signal of MPU under the condition that VMA of MPU is at "High" level.

#### Register Select (RS)

Input Pin No. 24

Register Select signal (RS) is used to select the address register and 18 control registers of the CRTC. When RS is at "Low" level, the address register is selected and when RS is at "High" level, control registers are selected. This signal is normally a derivative of the lowest bit (A0) of MPU address bus.

#### Enable (E)

Input Pin No. 23

Enable signal (E) is used as strobe signal in MPU Read/Write operation with the CRTC internal registers. This signal is normally a derivative of the HD6800 System  $\phi$ , clock.

#### Reset (RES)

Input Pin No. 2

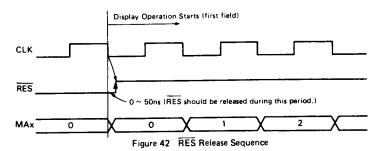

Reset signal (RES) is an input signal used to reset the CRTC.

When RES is at "Low" level, it forces the CRTC into the following status.

- All the counters in the CRTC are cleared and the device stops the display operation.

- 2) All the outputs go down to "Low" level.

- Control registers in the CRTC are not affected and remain unchanged.

This signal is different from other HD6800 family LSIs in the following functions and has restrictions for usage.

- RES has capability of reset function only when LPSTB is at "Low" level.

- The CRTC starts the display operation immediately after RES goes "High" level.

#### Interface Signals to CRT Display Device Character Clock (CLK)

Input Pin No. 21

CLK is a standard clock input signal which defines character timing for the CRTC display operation. CLK is normally derived from the external high-speed dot timing logic.

#### Horizontal Sync (HSYNC)

Output Pin No. 39

HSYNC is an active "High" level signal which provides horizontal synchronization for display device.

#### Vertical Sync (VSYNC)

Output Pin No. 40

VSYNC is an active "High" level signal which provides vertical synchronization for display device.

#### Display Timing (DISPTMG)

Output Pin No. 18

DISPTMG is an active "High" level signal which defines the display period in horizontal and vertical raster scanning. It is necessary to enable video signal only when DISPTMG is at "High" level.

#### Refresh Memory Address (MA<sub>0</sub> ~ MA<sub>13</sub>)

Output Pin No. 4 ~ 17)

$\rm MA_0 \sim MA_{13}$  are refresh memory address signals which are used to access to refresh memory is order to refresh the CRT screen periodically. These outputs enables 16k words max. refresh memory access. So, for instance, these are applicable up to 2000 characters/screen and 8-page system.

#### Raster Address (RA<sub>0</sub> ~ RA<sub>4</sub>)

Output Pin No. 38 ~ 34)

$RA_0\sim RA_4$  are raster address signals which are used to select the raster of the character generator or graphic pattern generator

#### Cursor Display (CUDISP)

Output Pin No. 19

CUDISP is an active "High" level video signal which is used to display the cursor on the CRT screen. This output is inhibited while DISPTMG is at "Low" level. Normally this output is mixed with video signal and provided to the CRT display device.

#### Light Pen Strobe (LPSTB)

Input Pin No. 3

LPSTB is an active "High" level input signal which accepts strobe pulse detected by the light pen and control circuit. When this signal is activated, the refresh memory address  $(MA_0 \sim MA_{13})$  which are shown in Fig. 2 are stored in the 14-bit light pen register. The stored refresh memory address need to be corrected in software, taking the delay time of the display device, light pen, and light pen control circuits into account.

#### ■ REGISTER DESCRIPTION

Table 1 Internal Registers Assignment

| <del>cs</del> | RS |   |   | ddr<br>egi: |     |     | Register | Register Name                | Program Unit                                 | READ | WRITE |     |     | -   | Data B | it       |     |          |     |

|---------------|----|---|---|-------------|-----|-----|----------|------------------------------|----------------------------------------------|------|-------|-----|-----|-----|--------|----------|-----|----------|-----|

| -             |    | 4 |   | 2           |     | _   | #        |                              |                                              |      |       | 7   | 6   | 5   | 4      | 3        | 2   | 1        | 0   |

| 1             | ×  | × | × | ×           | ×   | ×   |          |                              | -                                            |      | -     |     |     |     |        |          |     |          |     |

| 0             | 0  | × | × | ×           | ×   | : × | AR       | Address Register             | -                                            | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 0 | 0           | 0   | 0   | RO       | Horizontal Total *           | Character                                    | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 0 | 0           | 0   | 1   | R1       | Horizontal Displayed         | Character                                    | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 0 | 0           | 1   | 0   | R2       | Horizontal Sync*<br>Position | Character                                    | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 0 | 0           | 1   | 1   | R3       | Sync Width                   | Vertical-Raster,<br>Horizontal-<br>Character | ×    | 0     | wv3 | wv2 | wv1 | wvo    | wh3      | wh2 | wh1      | wh0 |

| 0             | 1  | 0 | 0 | 1           | (   | 0   | R4       | Vertical Total *             | Line                                         | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 0 | 1           | C   | ) 1 | R5       | Vertical Total Adjust        | Raster                                       | ×    | 0     |     |     |     |        |          | ļ   |          |     |

| 0             | 1  | 0 | 0 | 1           | 1   | 0   | R6       | Vertical Displayed           | Line                                         | ×    | 0     |     |     |     |        | <u> </u> |     |          | ļ   |

| 0             | 1  | 0 | 0 | 1           | 1   | 1   | R7       | Vertical Sync *<br>Position  | Line                                         | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 1 | 0           | C   | 0   | R8       | Interlace & Skew             | _                                            | ×    | 0     | C1  | CO  | D1  | D0     |          |     | ٧        | s   |

| 0             | 1  | 0 | 1 | 0           | C   | ) 1 | R9       | Maximum Raster<br>Address    | Raster                                       | ×    | 0     |     |     |     |        |          |     |          |     |

| 0             | 1  | 0 | 1 | 0           | 1   | 0   | R10      | Cursor Start Raster          | Raster                                       | ×    | 0     |     | В   | Р   |        |          |     |          |     |

| 0             | 1  | 0 | 1 | 0           | 1   | 1   | R11      | Cursor End Raster            | Raster                                       | ×    | 0     |     |     |     |        | :        | ļ   |          |     |

| 0             | 1  | 0 | 1 | 1           | (   | ) ( | R12      | Start Address(H)             | -                                            | 0    | 0     |     |     |     | -      |          |     | <u> </u> | _   |

| 0             | 1  | 0 | 1 | 1           | (   | 1   | R13      | Start Address(L)             | -                                            | 0    | 0     |     |     |     |        | !        |     | _        | ļ   |

| 0             | 1  | 0 | 1 | 1           |     |     | R14      | Cursor(H)                    | -                                            | 0    | 0     |     |     |     |        |          |     |          | ļ   |

| 0             | 1  | 0 | 1 | 1           |     | 1   | R15      | Cursor (L)                   | -                                            | 0    | 0     |     |     | 3   | ļ      |          | ļ   |          | ļ   |

| 0             | 1  | 1 | 0 | 0           | ) ( | 0   | R16      | Light Pen(H)                 | -                                            | 0    | ×     |     |     |     | ļ<br>+ |          | -   |          |     |

| 0             | 1  | 1 | 0 | C           | ) ( | ) 1 | R17      | Light Pen(L)                 | _                                            | 0    | ×     |     |     |     |        |          |     |          | İ   |

- [NOTE] 1. The Registers marked \*: (Written Value) = (Specified Value) 1

- 1. Written Value of R9 is mentioned below.

1. Non-interlace Mode | (Written Value) = (Specified Value) 1 interlace Sync Mode |

2. Interlace Sync & Video Mode | (Video Mode Value) = (Specified Value) |

3. Non-interlace Sync & Video Mode | (Video Mode Value) |

3. Non-interlace Sync & Video Mode | (Video Mode Value) |

3. Non-interlace Sync & Video Mode | (Video Mode Value) |

3. Non-interlace Sync & Video Mode | (Video Mode Value) |

3. Non-interlace Sync & Video Mode | (Video Mode Value) |

3. Non-interlace Mode | (Video Mode Value) |

4. Non-interlace Mode | (Video Mode Value) |

4. Non-interlace Mode | (Video Mode Value) |

4. Non-interlace Sync & (Video Mode Value) |

4. Non-interlace Sync

- (Written Value) = (Specified Value) -2

- 3. C0 and C1 specify skew of CUDISP.

DO and D1 specify skew of DISPTMG.

When S is "1", V specifies video mode. S specifies the Interlace Sync Mode.

4. B specifies the cursor blink. P specifies the cursor blink period.

- a specifies the cursor blink, it specifies the cursor blink period.

ww0~ww3 specify the bulse width of Vertical Sync Signal.

wh0~wh3 specify the pulse width of Horizontal Sync Signal.

R0 is ordinally programmed to be odd number in interlace mode.

O; Yes, x; No

#### ■ FUNCTION OF INTERNAL REGISTERS

#### Address Register (AR)

This is a 5-bit register used to select 18 internal control registers (RO~R17). Its contents are the address of one of 18 internal control registers. Programming the data from 18 to 31 produces no results. Access to RO~R17 requires, first of all, to write the address of corresponding control register into this register. When RS and  $\overline{CS}$  are at "Low" level, this register is selected.

#### Horizontal Total Register (R0)

This is a register used to program total number of horizontal characters per line including the retrace period. The data is 8-bit and its value should be programmed according to the specification of the CRT. When M is total number of characters, M-1 shall be programmed to this register. When programming for interlace mode, M must be even.

#### Horizontal Displayed Register (R1)

This is a register used to program the number of horizontal displayed characters per line. Data is 8-bit and any number that is smaller than that of horizontal total characters can be programmed.

#### Horizontal Sync Position Register (R2)

This is a register used to program horizontal sync position as multiples of the character clock period. Data is 8-bit and any number that is lower than the horizontal total number can be programmed. When H is character number of horizontal Sync Position, H-1 shall be programmed to this register. When programmed value of this register is increased, the display position on the CRT screen is shifted to the left. When programmed value is decreased, the position is shifted to the right. Therefore, the optimum horizontal position can be determined by this value.

#### Sync Width Register (R3)

This is a register used to program the horizontal sync pulse width and the vertical sync pulse width. The horizontal sync pulse width is programmed in the lower 4-bit as multiples of the character clock period. "0" can't be programmed. The vertical sync pulse width is programmed in higher 4-bit as multiples of the raster period. When "0" is programmed in higher 4-bit, 16 raster period (16H) is specified.

#### Vertical Total Register (R4)

This is a register used to program total number of lines per frame including vertical retrace period. The data is within 7-bit and its value should be programmed according to the specification of the CRTC. When N is total number of lines, N-1 shall be programmed to this register.

#### Vertical Total Adjust Register (R5)

This is a register used to program the optimum number to adjust total number of rasters per field. This register enables to decide the number of vertical deflection frequency more strictly.

#### Vertical Displayed Register (R6)

This is a register used to program the number of displayed character rows on the CRT screen. Data is 7-bit and any number that is smaller than that of vertical total characters can be programmed.

Table 2 Pulse Width of Vertical Sync Signal

|    | VS             | SW SW          |    |             |

|----|----------------|----------------|----|-------------|

| 27 | 2 <sup>6</sup> | 2 <sup>5</sup> | 24 | Pulse Width |

| 0  | 0              | 0              | 0  | 16H         |

| 0  | 0              | 0              | 1  | 1           |

| 0  | 0              | 1              | 0  | 2           |

| 0  | 0              | 1              | 1  | 3           |

| 0  | 1              | 0              | 0  | 4           |

| 0  | 1              | 0              | 1  | 5           |

| 0  | 1              | 1              | 0  | 6           |

| 0  | 1              | 1              | 1  | 7           |

| 1  | 0              | 0              | 0  | 8           |

| 1  | 0              | 0              | 1  | 9           |

| 1  | 0              | 1              | 0  | 10          |

| 1  | 0              | 1              | 1  | 11          |

| 1  | 1              | 0              | 0  | 12          |

| 1  | 1              | 0              | 1  | 13          |

| 1  | 1              | 1              | 0  | 14          |

| 1  | 1              | 1              | 1  | 15          |

H-Rester period

Table 3 Pulse Width of Horizontal Sync Signal

| 2³ | 2 <sup>2</sup> | 21 | 2° | Pulse Width |

|----|----------------|----|----|-------------|

| 0  | 0              | 0  | 0  | - (Note)    |

| 0  | 0              | 0  | 1  | 1 CH        |

| 0  | 0              | 1  | 0  | 2           |

| 0  | 0              | 1  | 1  | 3           |

| 0  | 1              | 0  | 0  | 4           |

| 0  | 1              | 0  | 1  | 5           |

| 0  | 1              | 1  | 0  | 6           |

| 0  | 1              | 1  | 1  | 7           |

| 1  | 0              | 0  | 0  | 8           |

| 1  | 0              | 0  | 1  | 9           |

| 1  | 0              | 1  | 0  | 10          |

| 1  | 0              | 1  | 1  | 11          |

| 1  | 1              | 0  | 0  | 12          |

| 1  | 1              | 0  | 1  | 13          |

| 1  | 1              | 1  | 0  | 14          |

| 1  | 1              | 1  | 1  | 15          |

CH; Character clock period (Note) HSW = "0" can't be used.

#### Vertical Sync Position Register (R7)

This is a register used to program the vertical sync position on the screen as multiples of the horizontal character line period. Data is 7-bit and any number that is equal to or less than vertical total characters can be programmed. When V is character number of vertical sync position, V-1 shall be programmed to this register. When programmed value of this register is increased, the display position is shifted up. When programmed value is decreased, the position is shifted down. Therefore, the optimum vertical position may be determined by this value.

#### Interlace and Skew Register (R8)

This is a register used to program raster scan mode and skew (delay) of CUDISP and DISPTMG.

#### Raster Scan Mode Program Bit (V, S)

Raster scan mode is programmed in the V, S bit.

Table 4 Raster Scan Mode (21, 20)

|   | S | Raster Scan Mode            |

|---|---|-----------------------------|

| 0 | 0 | Non-interlace Mode          |

| 1 | 0 | ) Non-Interface Wode        |

| 0 | 1 | Interlace Sync Mode         |

| 1 | 1 | Interlace Sync & Video Mode |

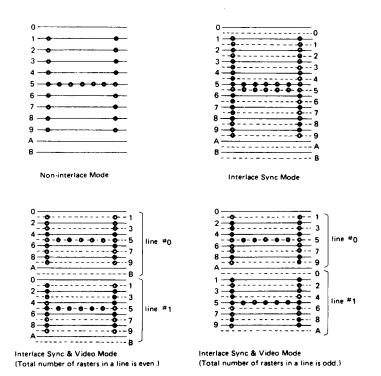

In the non-interlace mode, the rasters of even number field and odd number field are scanned duplicatedly. In the interlace sync mode, the rasters of odd number field are scanned in the middle of even number field. Then it is controlled to display the same character pattern in two fields. In the interlace sync & video mode, the raster scan method is the same as the interlace sync mode, but it is controlled to display different character pattern in two field.

#### Skew Program Bit (C1, C0, D1, D0)

These are used to program the skew (delay) of CUDISP and DISPTMG.

Skew of these two kinds of signals are programmed separately.

Table 5 DISPTMG Skew Bit (25, 24)

| D1 | D0 | DISPTMG            |  |

|----|----|--------------------|--|

| 0  | 0  | Non-skew           |  |

| 0  | 1  | One-character skew |  |

| 1  | 0  | Two-character skew |  |

| 1  | 1  | Non-output         |  |

Table 6 CUDISP Skew Bit (27, 26)

| C1 | C0 | CUDISP             |  |

|----|----|--------------------|--|

| 0  | 0  | Non-skew           |  |

| 0  | 1  | One-character skew |  |

| 1  | 0  | Two-character skew |  |

| 1  | 1  | Non-output         |  |

Skew function is used to delay the output timing of CUDISP and DISPTMG in LSI for the time to access refresh memory, character generator or pattern generator, and to make the same phase with serial video signal.

#### Maximum Raster Address Register (R9)\*

This is a register used to program maximum raster address within 5-bit. This register defines total number of rasters per character including line space. This register is programmed as

#### Non-interlace Mode, Interlace Sync Mode

When total number of rasters is RN, RN-1 shall be programmed.

#### Interlace Sync & Video Mode

When total number of rasters is RN, RN-2 shall be pro-

This manual defines total number of rasters in non-interlace mode, interlace sync mode and interlace sync & video mode as follows:

#### Non-interlace Mode

| 0 | Total Number of Rasters:5                     |

|---|-----------------------------------------------|

| 1 | Programmed Value: Nr = 4                      |

| 2 | The same as displayed total number of rasters |

| 3 | total number of rasters!                      |

|   |                                               |

#### Raster Address

#### Interlace Sync Mode

| 0              | Total Number of Rasters:5                               |

|----------------|---------------------------------------------------------|

| 0              | Programmed Value: Nr = 4                                |

| 1 1            | In the interlace sync mode,                             |

| 2              | /total number of rasters in                             |

| 32             | both the even and odd fields                            |

| <u></u>        |                                                         |

| 4 4            | is ten. On programming,<br>the half of it is defined as |

| Raster Address | total number of rasters.                                |

#### Interlace Sync & Video Mode

| 0 ———          | Total Number of Rasters:5   |

|----------------|-----------------------------|

| ,1             | Programmed Value: Nr = 3    |

| · 3            | /Total number of rasters    |

| 4              | displayed in the even field |

| Raster Address | and the odd field.          |

#### Cursor Start Raster Register (R10)

This is a register used to program the cursor start raster address by lower 5-bit  $(2^0 \sim 2^4)$  and the cursor display mode by higher 2-bit (25, 26).

Table 7 Cursor Display Mode (26, 25)

|   | - | Cursor Display Mode   |

|---|---|-----------------------|

|   |   |                       |

| 0 | 0 | Non-blink             |

| 0 | 1 | Cursor Non-display    |

| 1 | 0 | Blink 16 Field Period |

| 1 | 1 | Blink 32 Field Period |

Blink Period

16 or 32 Field Period

<sup>\*</sup>See Comparison of HD6845S and HD6845R on page 40.

#### Cursor End Raster Register (R11)

This is register used to program the cursor end raster address.

#### • Start Address Register (R12, R13)

These are used to program the first address of refresh memory to read out.

Paging and scrolling is easily performed using this register. This register can be read but the higher 2-bit  $(2^6, 2^7)$  of R12 are always "0".

#### • Cursor Register (R14, R15)

These two read/write registers stores the cursor location. The higher 2-bit (2<sup>6</sup>, 2<sup>7</sup>) of R14 are always "0".

#### • Light Pen Register (R16, R17)

These read only registers are used to catch the detection address of the light pen. The higher 2-bit  $(2^6, 2^7)$  of R16 are always "0". Its value needs to be corrected by software because there is time delay from address output of the CRTC to signal input LPSTB pin of the CRTC in the process that raster is lit after address output and light pen detects it. Moreover, delay time shown in Fig. 2 needs to be taken into account.

#### Restriction on Programming Internal Register

- 1) 0<Nhd<Nht + 1 ≤256

- 2)  $0 < \text{Nvd} < \text{Nvt} + 1 \le 128$

- 3)  $0 \le Nhsp \le Nht$

- 4)  $0 \le \text{Nvsp} \le \text{Nvt*}$

- 5) 0 ≤ NCSTART ≤ NCEND ≤ Nr (Non-interlace, Interlace sync mode)

- $0 \le N_{CSTART} \le N_{CEND} \le N_r + 1$  (Interlace sync & video mode)

- 6)  $2 \le N_r \le 30$  (Interlace Sync & Video mode)

- 7)  $3 \le Nht$  (Except non-interlace mode)

- $5 \le Nht$  (Non-interlace mode only)

- In the interlace mode, pulse width is changed ±½ raster time when vertical sync signal extends over two fields.

#### Notes for Use

The method of directly using the value programmed in the internal registers of LSI for controlling the CRT is adopted. Consequently, the display may flicker on the screen when the contents of the registers are changed from bus side asynchronously with the display operation.

#### **Cursor Register**

Writing into this register at frequent intervals for moving the cursor should be performed during horizontal and vertical retrace period.

#### Start Address Register

Writing into the start address register at frequent intervals for scrolling and paging should be performed during horizontal and vertical display period.

It is desirable to avoid programming other registers during display operation.

#### ■ OPERATION OF THE CRTC

#### Time Chart of CRT Interface Signals

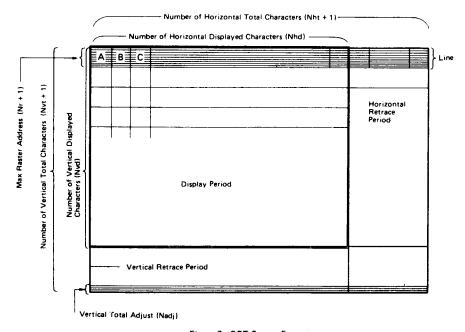

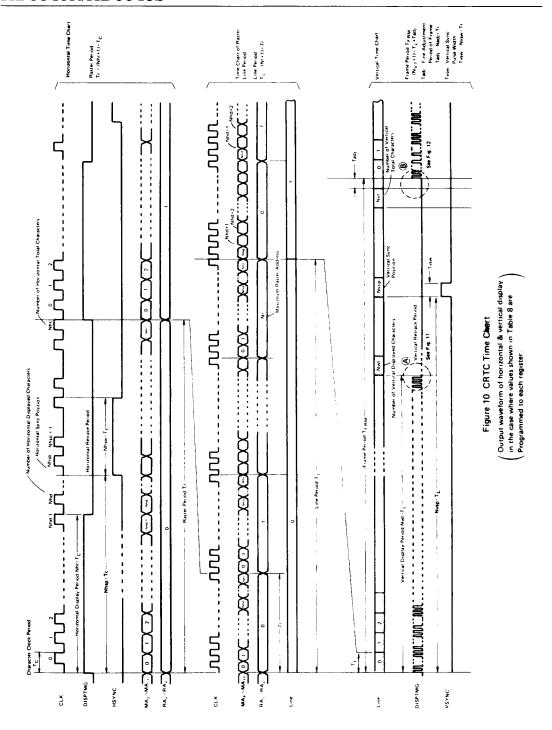

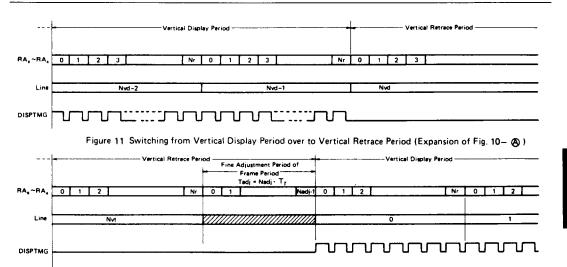

The following example shows the display operation in which values of Table 8 are programmed to the CRTC internal registers. Fig. 7 shows the CRT screen format. Fig. 10 shows the time chart of signals output from the CRTC.

Figure 7 CRT Screen Format

| Table 8 | Programmed | Values into | the | Registers |

|---------|------------|-------------|-----|-----------|

|         |            |             |     |           |

| Register | Register Name            | Value      | Register | Register Name       | Value |

|----------|--------------------------|------------|----------|---------------------|-------|

| RO       | Horizontal Total         | Nht        | R9       | Max Raster Address  | Nr    |

| R1       | Horizontal Displayed     | Nhd        | R10      | Cursor Start Raster |       |

| R2       | Horizontal Sync Position | Nhsp       | R11      | Cursor End Raster   |       |

| R3       | Sync Width               | Nvsw, Nhsw | R12      | Start Address (H)   | 0     |

| R4       | Vertical Total           | Nvt        | R13      | Start Address (L)   | 0     |

| R5       | Vertical Total Adjust    | Nadj       | R14      | Cursor (H)          |       |

| R6       | Vertical Displayed       | Nvd        | R15      | Cursor (L)          |       |

| R7       | Vertical Sync Position   | Nvsp       | R16      | Light Pen (H)       |       |

| R8       | Interlace & Skew         |            | R17      | Light Pen (L)       |       |

[NOTE] Nhd<Nht, Nvd<Nvt

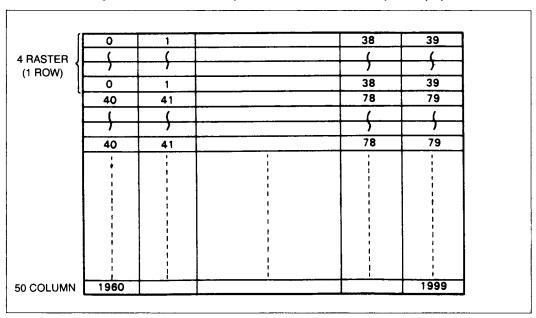

The relation between values of Refresh Memory Address  $(MA_0 \sim MA_{13})$  and Raster Address  $(RA_0 \sim RA_4)$  and the display position on the screen is shown in Fig. 16. Fig. 16 shows the case where the value of Start Address is 0.

#### • Interlace Control

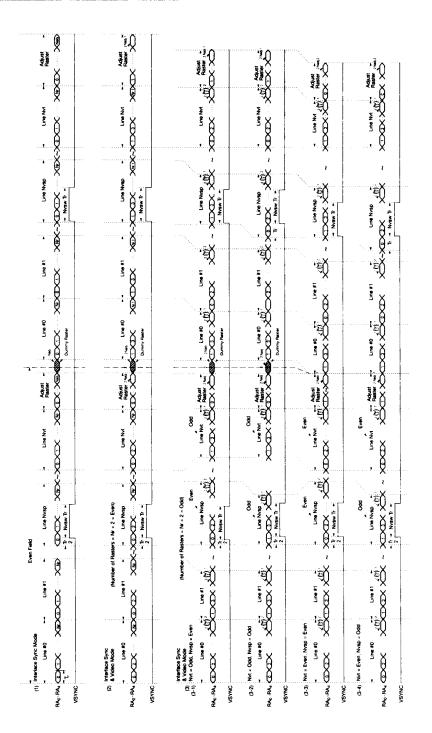

Fig. 8 shows an example where the same character is displayed in the non-interlace mode, interlace sync mode, and interlace sync & video mode.

Non-interlace Mode Control

In non-interlace mode, each field is scanned duplicatedly. The values of raster addresses  $(RA_0 \sim RA_4)$  are counted up one from 0.

#### Interlace Sync Mode Control

In the interlace sync mode, raster addressed in the even field and the odd field are the same as addressed in the non-interlace mode. One character pattern is displayed mutually and its displayed position in the odd field is set at 1/2 raster space down from that in the even field.

Figure 8 Example of Raster Scan Display

#### Interlace Sync & Video Mode Control

In interlace sync & video mode, the output raster address when the number of rasters is even is different from that when the number of rasters is odd.

Table 9 The Output of Raster Address in

|                                       | Interia                       | ice Sync & Video | Mode         |

|---------------------------------------|-------------------------------|------------------|--------------|

| Total<br>Numb<br>Raster               | Field<br>er of<br>s in a Line | Even Field       | Odd Field    |

| · · · · · · · · · · · · · · · · · · · | Even                          | Even Address     | Odd Address  |

|                                       | Even Line*                    | Even Address     | Odd Address  |

| Odd                                   | Odd Line*                     | Odd Address      | Even Address |

Internal line address begins from 0.

#### 1) Total number of rasters in a line is even;

When number of rasters is programmed to be even, even raster address is output in the even field and odd raster address is output in the odd field.

#### 2) Total number of rasters in a line is odd;

When total number of rasters is programmed to be odd, odd and even addresses are reversed according to the odd and even lines in each field. In this case, the difference in numbers of dots displayed between even field and odd field is usually smaller the case of 1). Then interlace can be displayed more stably.

[NOTE] The wide disparity of dots between number of dots between even field and odd field influences beam current of CRT. CRT, which has a stable high-voltage part, can make interlace display normal. On the contrary, CRT, which has unstable high-voltage part, moves deflection angle of beam current and also dots displayed in the even and odd fields may be shifted. Characters appears distroting on a border of the screen. So 2) programming has an effect to decrease such evil influences as mentioned above. Fig. 13 shows fine chart in each mode when interlace is performed.

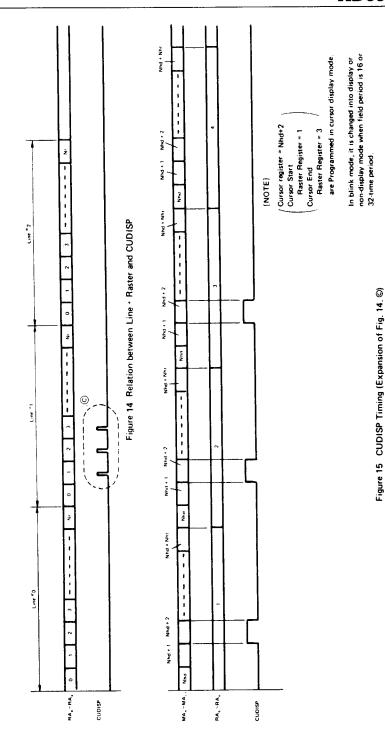

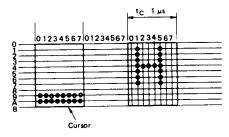

#### Cursor Control

Fig. 9 shows the display patterns where each value is programmed to the cursor start raster register and the cursor end raster register. Programmed values to the cursor start raster register and the cursor end raster register need to be under the following condition.

Cursor Start Raster Register ≤ Cursor End Raster Register ≤ Maximum Raster Address Register.

Time chart of CUDISP is shown in Fig. 14 and Fig. 15.

Cursor Start Address = 9 Cursor End Address = 10

Cursor Start Address = 1 Cursor End Address = 5

Figure 9 Cursor Control

Figure 12 Fine Adjustment Period of Frame in Vertical Display (Expansion of Fig. 10— (a))

Figure 13 Interlace Control

**(D)** HITACHI

programmed value of start address register is 0. Valid refresh memory address (0~Nvd-Nhd-1) during horizontal and Vertical retrace period. Refresh memory address are proyided even This is an example in the case where the are shown within the thick-line square. Nvd:11-NMd+NMr Ned-Mid+Mit New - New + New My - Mehd + Neh 2 Nhd + Nht 2Nhd + Nht Nhd + Nhr Horizontal Retrace Period MVG + 1) MVG-1 (NvG + 1) NNC Nvd+1)Nhd-1 (Nvd+1)Nhc (Next + 1) Mehd (Nort + 1) Meha (Nvr+2)Nhd-1 (Nvr+2) -Nhc Nvd Nho (Port + 1)PMG-1 Nvd ·Nhd · 1 Nvd · Nhd · 1 2Nhd-1 3Nhd.1 Horizontal Display Period Nvd-11-NMd+1 Nvd-Nhd+1 2MPd+1 N + PW Mvd : 1) - Nhd Mvd . Nhd Ĭ Vertical Display Period Renter address -Line number -

Figure 16 Refresh Memory Address (MA<sub>0</sub>~MA<sub>13</sub>)

#### ■ How to Use the CRTC

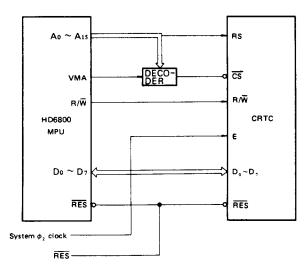

#### Interface to MPU

As shown in Fig. 17, the CRTC is connected with the standard bus of MPU to control the data transfer between them. The CRTC address is determined by  $\overline{CS}$  and RS, and the Read/Write operation is controlled by  $R/\overline{W}$  and E. When  $\overline{CS}$  is "Low" and RS is also "Low", the CRTC address register is selected. When  $\overline{CS}$  is "Low" and RS is "High", one of 18 internal regis-

ters is selected.

RES is the system reset signal. When RES becomes "Low", the CRTC internal control logic is reset. But internal registers shown in Table 1 (R0~R17) are not affected by RES and remain unchanged.

The CRTC is designed so as to provide an interface to microcomputers, but adding some external circuits enables an interface to other data sources.

Figure 17 Interface to MPU

#### Dot Timing Generating Circuit

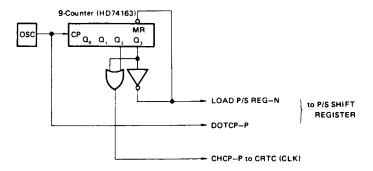

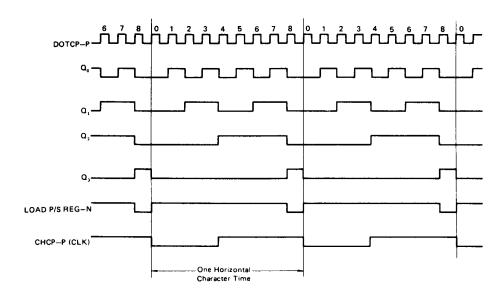

CRTC's CLK input (21 pin) is provided with CLK which defines horizontal character time period from the outside. This CLK is generated by dot counter shown in Fig. 18. Fig. 18 shows a example of circuit where horizontal dot number of the character is "9". Fig. 19 shows the operation time chart

of dot counter shown in Fig. 18. As this example shows explicitly, CLK is at "Low" level in the former half of horizontal character time and at "High" level in the latter half. It is necessary to be careful so as not to mistake this polarity.

Figure 18 Example of Dot Counter

Figure 19 Time Chart of Dot Counter

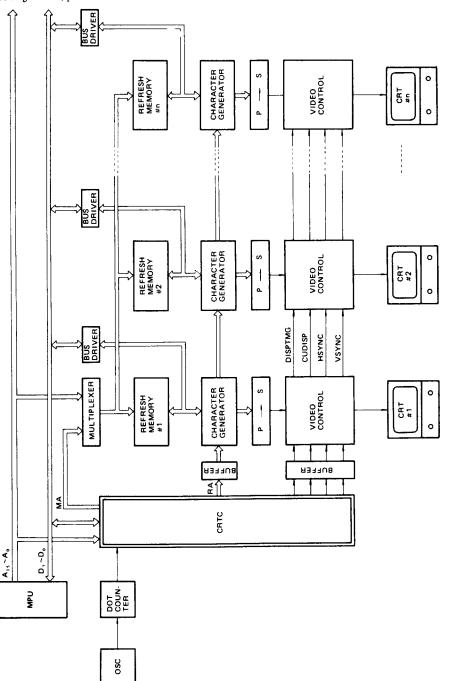

#### ■ INTERFACE TO DISPLAY CONTROL UNIT

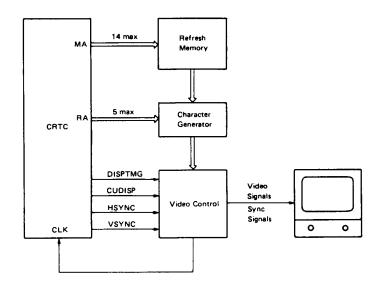

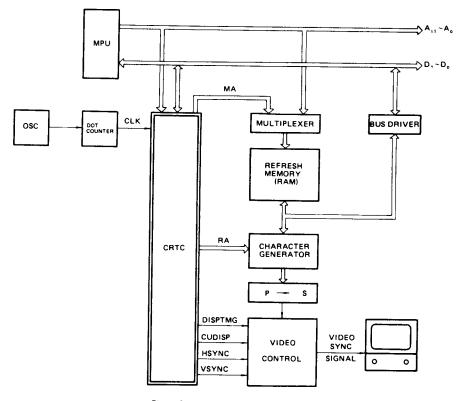

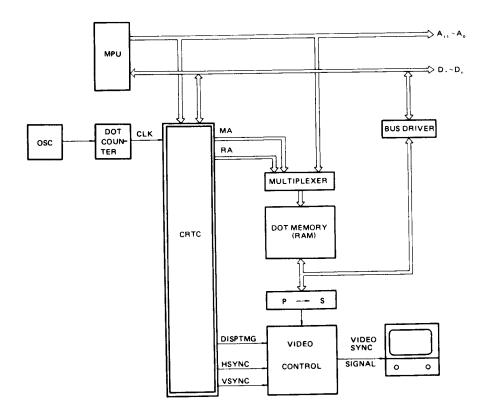

Fig. 20 shows the interface between the CRTC and display control unit. Display control unit is mainly composed of Refresh Memory, Character Generator, and Video Control circuit. For refresh memory, 14 Memory Address line (0~16383) max are provided and for character generator, 5 Raster Address line (0~31) max are provided. For video control circuit, DISPTMG, CUDISP, HSYNC, and VSYNC are sent out. DISPTMG is used to control the blank period of video signal. CUDISP is used as video signal to display the cursor on the CRT screen. Moreover, HSYNC and VSYNC are used as drive signals respectively for CRT horizontal and vertical deflection circuits.

Outputs from video control circuit, (video signals and sync signals) are provided to CRT display unit to control the deflection and brightness of CRT, thus characters are displayed on the screen.

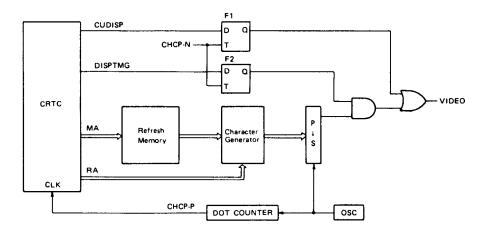

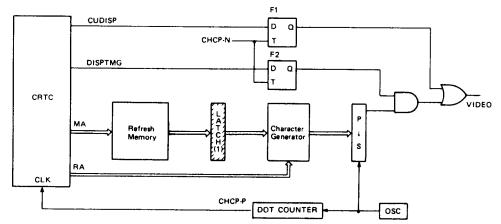

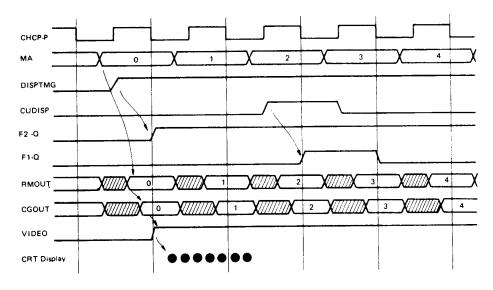

Fig. 21 shows detailed block diagram of display control unit. This shows how to use CUDISP and DISPTMG. CUDISP and DISPTMG should be used being latched at least one time at external flip-flop F1 and F2. Flip-flop F1 and F2 function to make one-character delay time so as to synchronize them with video signal from parallel-serial converter. High-speed D type flip-flop as TTL is used for this purpose. After being delayed at F1 and F2 DISPTMG is AND-ed with character video signal, and CUDISP is Or-ed with output from AND gate. By using this circuitry, blanking of horizontal and vertical retrace time is controlled. And cursor video is mixed with character video signal.

Fig. 21 shows the example in the case that both refresh memory and Character Generator can be accessed for horizontal one character time. Time chart for this case is shown in Fig. 24. This method is used when a few character needed to be displayed in horizontal direction on the screen.

Figure 20 Interface to Display Control Unit

Figure 21 Display Control Unit (1)

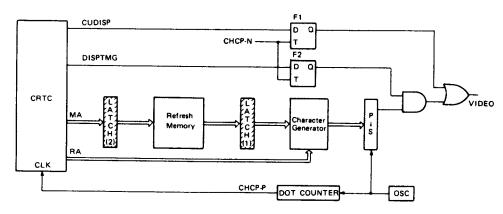

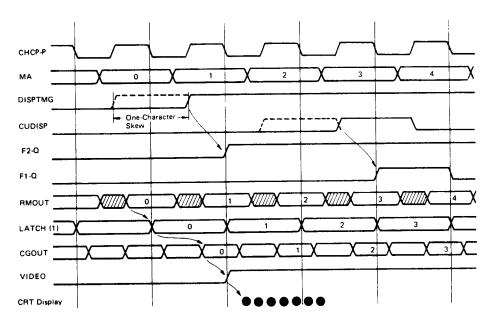

When many characters are displayed in horizontal direction on the screen, and horizontal one-character time is so short that both refresh memory and Character Generator cannot be accessed, the circuitry shown in Fig. 22 should be used. In this case refresh memory output shall be latched and Character Generator shall be accessed at the next cycle. The time chart in this case is shown in Fig. 25. CUDISP and DISPTMG should be provided after being delayed by one-character time by using skew bit of interlace & skew register (R8). Moreover, when

there are some troubles about delay time of MA during horizontal one-character time on high-speed display operation, system shown in Fig. 23 is adopted. The time chart in this case is shown in Fig. 26. Character video signal is delayed for two-character time because each MA outputs and refresh memory outputs are latched, and they are made to be in phase with CUDISP and DISPTMG by delaying for two-character time. Table 10 shows the circuitry selection standard of display units.

Table 10 Circuitry Standard of Display Control Unit

| Case | Relation among t <sub>CH</sub> Refresh Memory and Character Generator                     | Block   | Interlace & Skew Register<br>Bit Programming |    |    |    |  |  |  |

|------|-------------------------------------------------------------------------------------------|---------|----------------------------------------------|----|----|----|--|--|--|

|      |                                                                                           | Diagram | C1                                           | CO | D1 | DO |  |  |  |

| 1    | t <sub>CH</sub> > RM Access + CG Access + t <sub>MAD</sub>                                | Fig. 21 | 0                                            | 0  | 0  | 0  |  |  |  |

| 2    | RM Access + CG Access + t <sub>MAD</sub> ≥ t <sub>CH</sub> > RM Access + t <sub>MAD</sub> | Fig. 22 | 0                                            | 1  | 0  | 1  |  |  |  |

| 3    | RM Access + $t_{MAD} \ge t_{CH} > RM$ Access                                              | Fig. 23 | 1                                            | 0  | 1  | 0  |  |  |  |

t<sub>CH</sub>: CHCP Period; t<sub>MAD</sub>: MA Delay

RM: Refresh Memory CG: Character Generator

Figure 22 Display Control Unit (2)

Figure 23 Display Control Unit (For high-speed display operation) (3)

Figure 24 Time Chart of Display Control Unit (1)

Figure 25 Time Chart of Display Control Unit (2)

Figure 26 Time Chart of Display Unit (3)

Table 10A Parameter of Display

|                                 | Specification of CRT monitor | Display Configurations | CRTC Internal Register |

|---------------------------------|------------------------------|------------------------|------------------------|

| Character Dot Size (Horizontal) |                              | 0                      | External Circuit       |

| Character Dot Size (Vertical)   |                              | 0                      | R9                     |

| Horizontal Total                | 0                            |                        | R0                     |

| Horizontal Displayed            | Δ                            | 0                      | R1                     |

| Horizontal Sync Position        | 0                            |                        | R2                     |

| Horizontal Sync Width           | 0                            |                        | R3                     |

| Vertical Total                  | 0                            |                        | R4                     |

| Vertical Displayed              | Δ                            | 0                      | R6                     |

| Vertical Sync Width             | 0                            |                        | F3                     |

| Interface mode                  |                              | 0                      | R8                     |

| Skew                            | Δ                            | 0                      | R8                     |

| Cursor Size                     |                              | 0                      | R10, R110              |

| Start Address                   |                              | 0                      | R12, R13               |

| Cursor Address                  |                              | 0                      | R14, F15               |

$<sup>\</sup>triangle$  This parameter is decided by specification of CRT monitor.

#### ■ HOW TO DECIDE PARAMETERS SET ON THE CRTC

#### How to Decide Parameters Based on Specification of CRT Display Unit (Monitor)

#### **Number of Horizontal Total Characters**

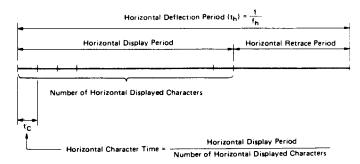

Horizontal deflection frequency <sup>fh</sup> is given by specification of CRT display unit. Number of horizontal total characters is determined by the following equation.

$$f_h = \frac{1}{t_C (N_{ht} + 1)}$$

where,

tc : Cycle Time of CLK (Character Clock)

Nht: Programmed Value of Horizontal Total Register

#### Number of Vertical Total Characters

Vertical deflection frequency is given by specification of CRT display unit. Number of vertical Total characters is determined by the following equation.

1) Non-interlace Mode

$$Rt = (Nvt + 1)(Nr + 1) + Nadj$$

2) Interlace Sync Mode

$$Rt = (Nvt + 1)(Nr + 1) + Nadj + 0.5$$

3) Interlace Sync & Video Mode

$$Rt = \frac{(Nvt + 1)(Nr + 2) + 2Nadj + 1}{2}$$

is applied when both total numbers of vertical character

(a) is applied when both total numbers of vertical characters (Nvt + 1) and that of rasters in a line (Nr + 2) are odd.

(b) is applied when total number of rasters (Nr + 2) is even, or when (Nr + 2) is odd and total number of vertical characters (Nvt + 1) is even.

where,

Rt : Number of Total Rasters per frame

(Including retrace period)

: Programmed Value of Vertical Total

Register (R4)

$Rt = \frac{(Nvt + 1)(Nr + 2) + 2Nadj}{2}$

Nr : Programmed Value of Maximum Raster

Address Register (R9)

Nadj: Programmed Value of Vertical Total Adjust

Register (R5)

#### Horizontal Sync Pulse Width

Horizontal sync pulse width is programmed to low order 4-bit of horizontal sync width register (R3) in unit of horizontal character time. Programmed value can be selected within from 1 to 15.

#### **Horizontal Sync Position**

As shown in Fig. 27, horizontal sync position is normally selected to be in the middle of horizontal retrace period. But there are some cases where is optimum sync position is not located in the middle of horizontal retrace period according to specification of CRT. Therefore, horizontal sync position should be determined by specification of CRT. Horizontal sync pulse position is programmed in unit of horizontal character time.

Figure 27 Time Chart of HSYNC

#### Vertical Sync Pulse Width

Vertical Sync Pulse Width is programmed to high order 4-bit of vertical sync pulse width register (R3) in unit of raster period. Programmed value can be selected within from 1 to 16.

#### Vertical Sync Position

As shown in Fig. 28, vertical sync position is normally selected to be in the middle of vertical retrace period. But there are some cases where its optimum sync position is not located in the middle of vertical retrace period according to specification of CRT. Therefore, vertical sync position should be determined by specification of CRT. Vertical sync pulse position is programmed to vertical sync position register (R7) in unit of line period.

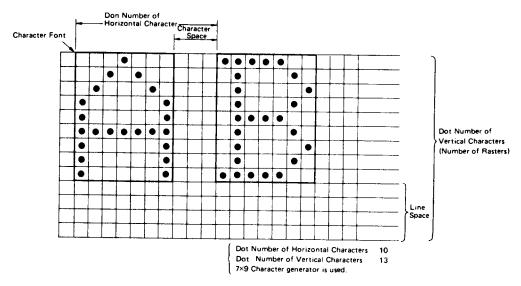

#### How to Decide Parameters Based on Screen Format Dot Number of Characters (Horizontal)

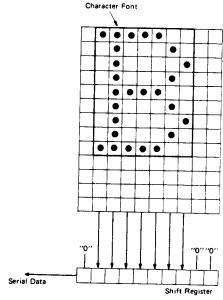

Dot number of characters (horizontal) is determined by character font and character space. An example is shown in Fig. 29. More strictly, dot number of characters (horizontal) N is determined by external N-counter. Character space is set by means shown in Fig. 30.

#### Dot Number of Characters (Vertical)

Dot number of characters (vertical) is determined by characters font and line space. An example is shown in Fig. 29. Dot number of characters (vertical) is programmed to maximum raster address (R9) of CRTC.

Figure 28 Time Chart of VSYNC

Figure 29 Dot Number of Horizontal and Vertical Characters

Figure 30 How to Make Character Space

#### **Number of Horizontal Displayed Characters**

Number of horizontal displayed characters is programmed to horizontal displayed register (R1) of the CRTC. Programmed value is based on screen format. Horizontal display period, which is given by specification of horizontal deflection frequency and horizontal retrace period of CRT display unit, determines horizontal character time, being divided by number of horizontal displayed characters. Moreover, its cycle time and access time which are necessary for CRT display system are determined by horizontal character time.

#### **Number of Vertical Displayed Characters**

Number of vertical displayed characters is programmed to vertical displayed register (R6). Programmed value is based on screen format. As specification of vertical deflection frequency of CRT determines number of total rasters (Rt) including verti-

cal retrace period and the relation between number of vertical displayed character and total number of rasters on a screen is as mentioned above, CRT which is suitable for desired screen format should be selected.

For optimum screen format, it is necessary to adjust number of rasters per line, number of vertical displayed characters, and total adjust raster (Nadj) within specification of vertical deflection frequency.

#### Scan Mode

The CRTC can program three-scan modes shown in Table 11 to interlace mode register (R8). An example of character display in each scan mode is shown in Fig. 8.

Figure 31 Number of Horizontal Displayed Characters

Table 11 Program of Scan Mode

| ٧                                            | S         | Scan Mode                 | Main Usage                                                                   |

|----------------------------------------------|-----------|---------------------------|------------------------------------------------------------------------------|

| 0                                            | 0         | Non-interded              | Normal Display of Characters                                                 |

| Non-interlace  Non-interlace  Interlace Sync | & Figures |                           |                                                                              |

| 0                                            | 1         | Interlace Sync            | Fine Display of Characters<br>& Figures                                      |

| 1                                            | 1         | Interlace Sync<br>& Video | Display of Many Characters<br>& Figures Without Using<br>High-resolution CRT |

[NOTE] In the interlace mode, the number of times per sec. in raster scanning on one spot on the screen is half as many as that in non-interlace mode. Therefore, when persistence of luminescence is short, flickering may happen. It is necessary to setect optimum scan mode for the system, taking characteristics of CRT, raster scan speed, and number of displayed characters and figures into account.

#### **Cursor Display Method**

Cursor start raster register and cursor end raster register

(R10, R11) enable programming the display modes shown in Table 7 and display patterns shown in Fig. 9. Therefore, it is possible to change the method of cursor display dynamically according to the system conditions as well as to realize the cursor display that meets the system requirements.

#### Start Address

Start address resisters (R12, R13) give an offset to the address of refresh memory to read out. This enables paging and scrolling easily.

#### Cursor Register

Cursor registers (R14, R15) enable programming the cursor display position on the screen. As for cursor address, it is not X, Y address but linear address that is programmed.

#### Applications of the CRTC

#### Monochrome Character Display

Fig. 32 shows a system of monochrome character display. Character clock signal (CLK) is provided to the CRTC through OSC and dot counter. It is used as basic clock which drives internal control circuits. MPU is connected with the CRTC by standard bus and controls the CRTC initialization and read/write of internal registers.

Refresh memory is composed of RAM which has capacity of one frame at least and the data to be displayed is coded and stored. The data to refresh memory is changed through MPU

Figure 32 Monochrome Character Display

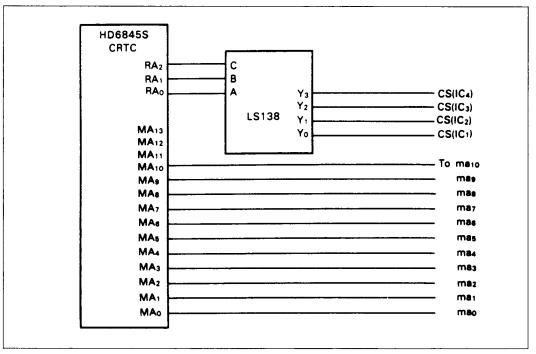

bus, while refresh memory is read out successively by the CRTC to display a static pattern on the screen. Refresh memory is accessed by both MPU and the CRTC, so it needs to change its address selectively by multiplexer. The CRTC has 14 MA (Memory Address output), but in fact some of them that are needed are used according to capacity of refresh memory.

Code output of refresh memory is provided to character generator. Character generator generates a dot pattern of a specified raster of a specified character in parallel according to code output from refresh memory and RA (Raster Address output) from the CRTC. Parallel-serial converter is normally composed of shift register to convert output of character generator into a serial dot pattern. Moreover, DISPTMG.

CUDISP, HSYNC, and VSYNC are provided to video control circuit. It controls blanking for output of parallel-serial converter, mixes these signals with cursor video signal, and generates sync signals for an interface to monitor.

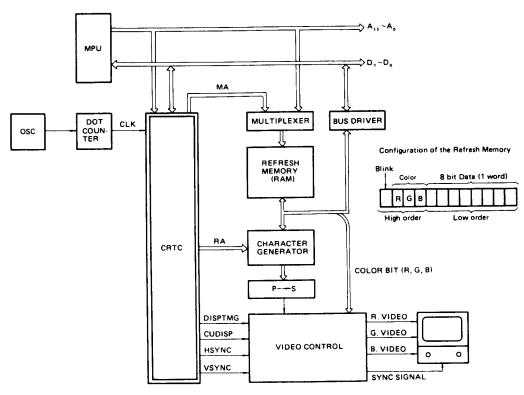

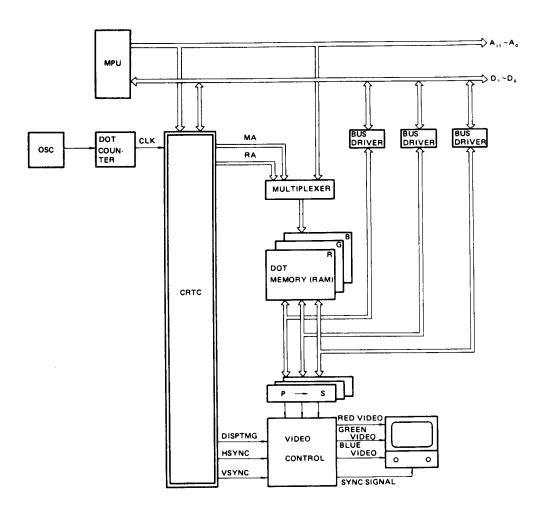

#### Color Character Display

Fig. 33 shows a system of color character display. In this example, a 3-bit color control bit (R, G, B) is added to refresh memory in parallel with character code and provided to video control circuit. Video control controls coloring as well as blanking and provides three primary color video signals (R, G, B signals) to CRT display device to display characters in seven kinds of color on the screen.

Figure 33 Color Character Display

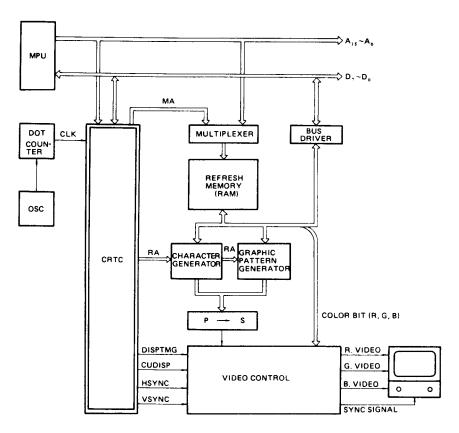

#### • Color limited Graphic Display

Limited graphic display is to display simple figures as well as character display by combination of picture element which are defined in unit of one character.

As shown in Fig. 34, graphic pattern generator is set up in parallel with character generator and output of these generators are wire-ORed. Which generator is accessed depends on

coded output of refresh memory.

In this example, graphic pattern generator adopts ROM, so only the combination of picture elements which are programmed to it is used for this graphic display system. Adopting RAM instead of ROM enables dynamically writable symbols in any combination on one display by changing the contents of them.

Figure 34 Color Limited Graphic Display

#### Monochrome Full Graphic Display

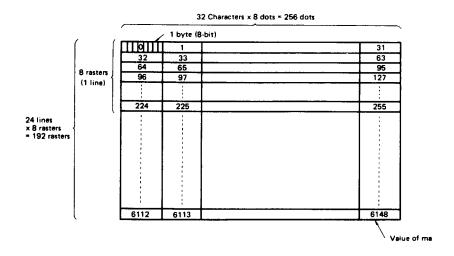

Fig. 35 shows a system of monochrome full graphic display. While simple graphic display is figure display by combination of picture elements in unit of 1 picture elements, full graphic display is display of any figures in unit of 1 dot. In this case,

refresh memory is dot memory that stores all the dot patterns, so its output is directly provided to parallel-serial converter to be displayed. Dot memory address to refresh the screen is set up by combination of MA and RA of CRTC.

Figure 35 Monochrome Full Graphic Display

Fig. 36 shows an example of access to refresh memory by combination of MA and RA. Fig. 36 shows a refresh memory address method for full graphic display. Correspondence between dot on the CRT screen and refresh memory address is shown in Fig. 37.

Figure 36 Refresh Memory Address Method for Full Graphic Display

Figure 37 Memory Address and Dot Display Position on the Screen for Full Graphic Display

#### Color Full Graphic Display

Fig. 38 shows a system of color full graphic display by 7-color display. Refresh memory is composed of three dot memories which are respectively used for red, green, and blue. These dot memories are read out in parallel at one time and

their output is provided to three parallel-serial converters. Then video control circuit adds the blanking control to output of these converters and provides it to CRT display device as red, green, and blue video signals with sync signals.

Figure 38 Color Full Graphic Display

Figure 38-A Refresh Memory Address Method for Full Graphic Display

Figure 38-B Memory Address and Dot Display Position on the Screen for Full Graphic Display

#### Cluster Control of CRT Display

The CRTC enables cluster control that is to control CRT display of plural devices by one CRTC. Fig. 39 shows a system of cluster control. Each display control unit has refresh memory, character generator, parallel-serial converter, and video control

circuit separately, but these are controlled together by the CRTC

In this system, it is possible for plural CRT display devices to have their own display separately.

Figure 39 Cluster Control by the CRTC

#### ■ EXAMPLES OF APPLIED CIRCUIT OF THE CRTC

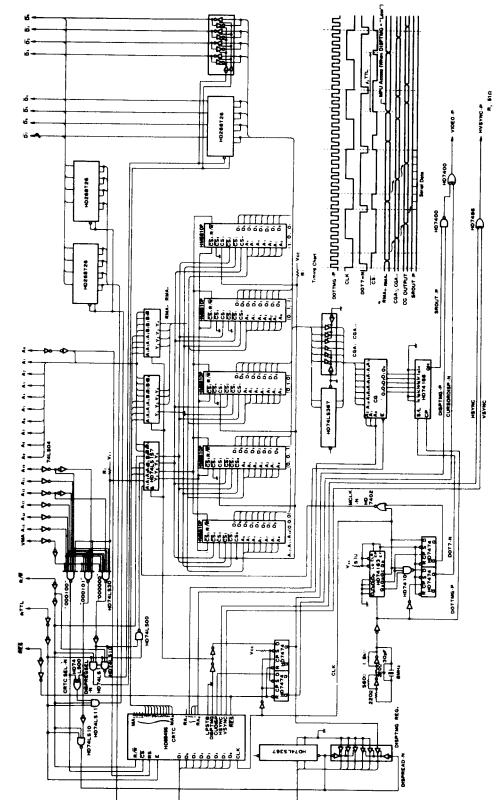

Fig. 41 shows an example of application of the CRTC to monochrome character display. Its specification is shown in

Table 12. Moreover, specification of CRT display unit is shown in Table 13 and initializing values for the CRTC are shown in Table 14.

Table 12 Specification of Applied Circuit

| Item                            |                                           | Sp   | ecifi | catio | n     |       |     |      |                |    |                |                |                |                       |                |    |    |

|---------------------------------|-------------------------------------------|------|-------|-------|-------|-------|-----|------|----------------|----|----------------|----------------|----------------|-----------------------|----------------|----|----|

| Character Format                | 5 × 7 Dot                                 |      |       |       |       |       |     |      |                |    |                |                |                |                       |                |    |    |

| Character Space                 | Horizonta                                 | 1:3  | Dot   | Vert  | ical  | : 5 0 | ot  |      |                |    |                |                |                | •                     |                |    |    |

| One Character Time              | 1 μs                                      |      |       |       |       |       |     |      |                |    |                |                |                |                       |                |    |    |

| Number of Displayed Characters  | 40 characters × 16 lines = 640 characters |      |       |       |       |       |     |      |                |    |                |                |                |                       |                |    |    |

| Access Method to Refresh Memory | Snychronous Method (DISPTMG Read)         |      |       |       |       |       |     |      |                |    |                |                |                |                       |                |    |    |

| Refresh Memory                  | 640 B                                     |      |       |       |       |       |     |      |                |    |                |                |                |                       |                |    |    |

|                                 |                                           | 215  | 214   | 213   | 212   | 211   | 210 | 29   | 2 <sup>8</sup> | 27 | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | 2 <sup>2</sup> | 21 | 2º |

|                                 | Refresh<br>Memory                         | 0    | 0     | 0     | 0     | 0     | 0   | •    | •              | •  | •              |                | *              | •                     | •              | •  | •  |

| Address Map                     | CRTC<br>Address<br>Register               | 0    | 0     | 0     | 1     | 0     | 0   | *    | ×              | >  | ×              | *              |                | *                     | *.             | ×  | 0  |

|                                 | CRTC<br>Control<br>Register               | 0    | 0     | 0     | 1     | 0     | 0   | ę    |                | `  |                | ×              | ۸.             |                       | *              | ×  | 1  |

|                                 |                                           | ×·   | ٠٠d   | on't  | care, | ٠.    | 0   | or 1 |                |    |                |                |                |                       |                |    |    |

| Synchronization Method          | HVSYNC                                    | Meth | od    |       |       | -     |     |      |                |    |                |                |                |                       |                |    |    |

Table 13 Specification of Character Display

| Item                                        | Specification                        |  |

|---------------------------------------------|--------------------------------------|--|

| Scan Mode                                   | Non-interface                        |  |

| Horizontal Deflection Frequency             | 15.625 kHz                           |  |

| Vertical Deflection Frequency               | 60.1 Hz                              |  |

| Dot Frequency                               | 8 MHz                                |  |

| Character Dot (Horizontal × Vertical)       | 8 × 12 (Character Font 5 × 7)        |  |

| Number of Displayed Characters (Row x Line) | 40 × 16                              |  |

| HSYNC Width                                 | 4 μs                                 |  |

| VSYNC Width                                 | 3 H                                  |  |

| Cursor Display                              | Raster 9 ~ 10, Blink 16 Field Period |  |

| Paging, Scrolling                           | Not used                             |  |

| Register | Name                     | Symbol        | Initializing Value<br>Hex (Decimal) |      |

|----------|--------------------------|---------------|-------------------------------------|------|

| R0       | Horizontal Total         | Nht           | 3F                                  | (63) |

| R1       | Horizontal Displayed     | Nhd           | 28                                  | (40) |

| R2       | Horizontal Sync Position | Nhsp          | 34                                  | (52) |

| R3       | Sync Width               | Nvsw, Nhsw    | 34                                  |      |

| R4       | Vertical Total           | Nvt           | 14                                  | (20) |

| R5       | Vertical Total Adjust    | Nadj          | 08                                  | ( 8) |

| R6       | Vertical Displayed       | Nvd           | 10                                  | (16) |

| R7       | Vertical Sync Position   | Nvsp          | 13                                  | (19) |

| R8       | Interlace & Skew         |               | 00_                                 |      |

| R9       | Maximum Raster Address   | Nr            | 0B                                  | (11) |

| R10      | Cursor Start Raster      | B, P, NCSTART | 49                                  |      |

| R11      | Cursor End Raster        | NCEND         | 0A                                  | (10) |

| R12      | Start Address (H)        |               | 00                                  | ( 0) |

| R13      | Start Address (L)        |               | 00                                  | ( 0) |

| 314      | Cursor (H)               |               | 00                                  | ( 0) |

| R15      | Cursor (L)               |               | 00                                  | ( 0) |

Table 14 Initializing Values for Character Display

Figure 40 Non-interlace Display (Example)

Figure 41 Example of Applied Circuit of the CRTC (Monochrome Character Display)

118

- DISPLAY SEQUENCE AFTER RES RELEASE OF HD6845S (1) HD6845S starts the display operation immediately after the release of RES. The operation at the first field is different from the normal subsequent display operation. [Operation at the first field after the RES release]

- "Low" level. The display is inhibited.) The data programmed in the start address register is not

DISPTMG and CUDISP are not output. (They remain at

- used. (MA and RA start at "0".)

- The sequences are shown in the following figures. (3)

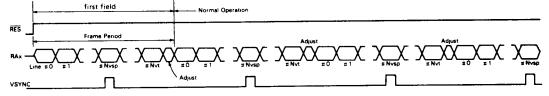

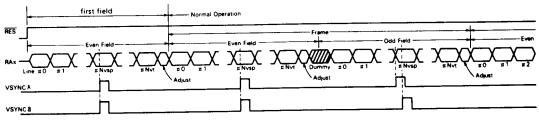

Figure 43 RES Release Sequence in The Non-interlace Mode

Interlace Sync Control VSYNC-A Interface Sync & Video Control (Nr+2=Even) Interlace Sync & Video Control (Nr+2=Odd, Nvt=Odd, Nvsp=Even) Interface Sync & Video Control (Nr+2=Odd, Nvt=Odd, Nvsp=Odd)

Figure 44 RES Release Sequence in The Interlace Mode (1)

Interlace Sync & Video Control (Nr+2=Odd, Nvt=Even, Nvsp=Even) VSYNCC : Interface Sync & Video Control (Nr+2=Odd, Nvt=Even, Nvsp=Odd)

Figure 45 RES Release Sequence in The Interlace Mode (2)

#### ■ ANOMALOUS OPERATIONS IN HD6845S CAUSED BY REWRITING REGISTERS DURING THE DISPLAY OPERATION®

| Register<br># | Register Name               | Anomalous operations caused by rewriting registers & Conditions to avoid those operations                                                                                                                                                                                                                                                                                                                                               | Rewriting** OK or NG |

|---------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| R0            | Horizontal Total            | The horizontal scan period is disturbed.                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| R1            | Horizontal Displayed        | There are some cases where the width of DISPTMG becomes shorter than the programmed value at the moment of a rewrite operation. An error operation occurs only during one raster period.                                                                                                                                                                                                                                                |                      |

| R2            | Horizontal<br>Sync Position | There are some cases where HSYNC is placed on the position different from the programmed value or the noise is output.                                                                                                                                                                                                                                                                                                                  | ×                    |

| R3            | Sync Width                  | When a rewrite operation is performed at a "High" level on HSYNC pulse or VSYNC pulse, there are some cases where the width pulse becomes shorter than the programmed value at the moment of a rewrite operation.                                                                                                                                                                                                                       | Δ                    |

| R4            | Vertical Total              | al When a rewrite operation is performed during the last raster period in the line, there is<br>a possibility that the disturbance occurs during the vertical scan period. There is no<br>problem of a rewrite operation during raster period except this period.                                                                                                                                                                       |                      |

| R5            | Vertical Total<br>Adjust    | When a rewrite operation is performed in the last character time of the raster period, there are some cases where the numbers of Adjust Raster, specified by program, are not added. (Only during the adjust raster period)                                                                                                                                                                                                             |                      |

| R6            | Vertical Displayed          | After the moment of a rewrite operation, there are some cases where the Display is inhibited. However, the display according to the programmed value is performed from the next field.                                                                                                                                                                                                                                                  |                      |